프로젝트 제작

Example - CLK 기반 LED 주기적으로 ON / OFF

module example1#(

parameter N = 25

)(

input wire clk,

input wire rstn,

output wire out

);

reg [N-1:0] count;

always @(posedge clk, negedge rstn) begin

if (~rstn) count <= {N{1'b0}};

else count <= count + 1'b1;

end

assign out = count[N-1];

endmoduleLED의 작동이 매우 빠르기 때문에 Count의 MSB가 1일때 켜고 0일때 꺼지도록 설계

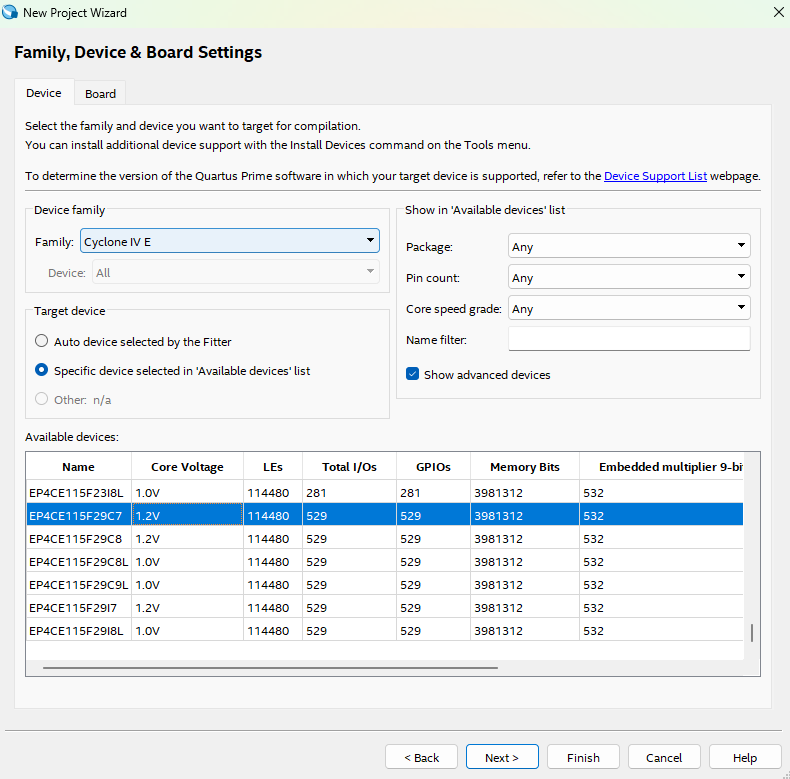

Quartus Settings

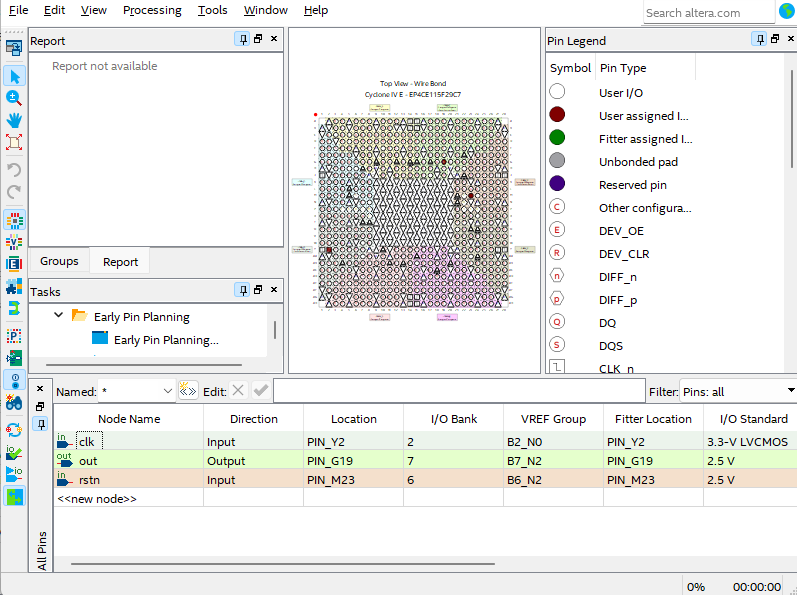

Analasys 를 진행 후에 Pin Planning

Pin Planning은 Reference File을 보고 각 PIN의 이름과 전압을 설정

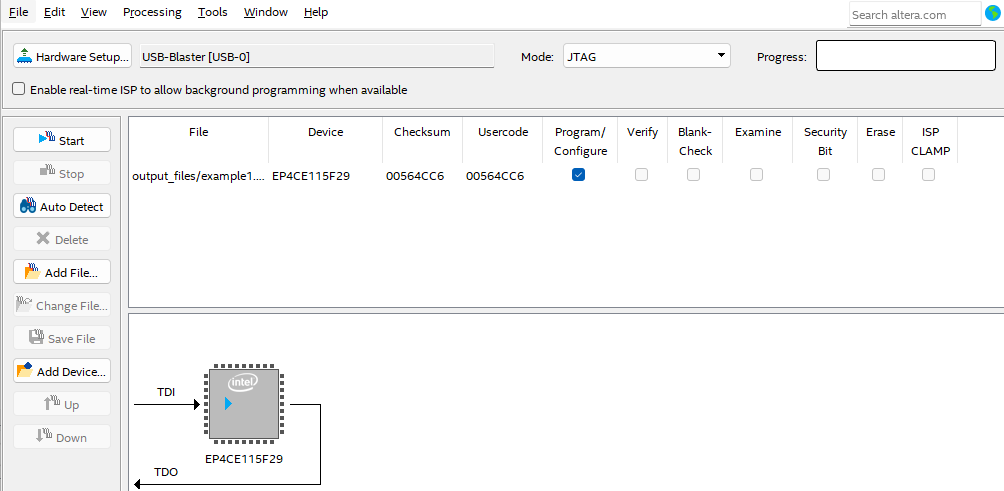

Synthesis까지 진행 후에 Programmer에 들어가서 FPGA 보드에 업로드